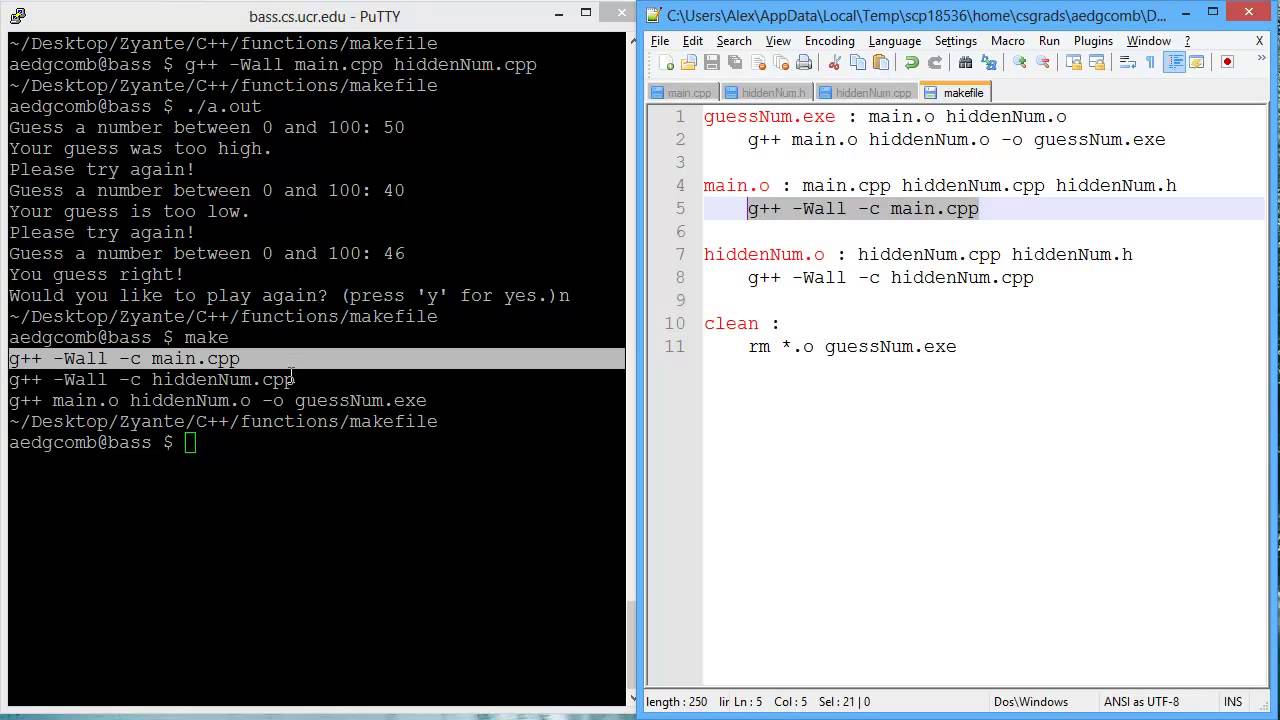

Показать больше: experienced vb6 developer modify existing vb6 project, review existing software project upgrade, opening existing vb6 project, makefile example c, makefile for c program in linux, how to use c++ on netbeans, netbeans c tutorial, c++ makefile generator, netbeans c, netbeans generate makefile, how to run makefile in c, adding login member section existing website, payroll project visual cpp class, 12th class fee management project, changing dpi existing psd project, i need to make a website project, You may work in the same teams as you did the in-class presentations. Note: the make file builds successfully the old main, all I need is integration with C++. configure the makefile to work with the new main add that contains main() function, and call run() from it The second target label ‘clean’ removes all the files with the name ‘myprogram’. In the above makefile, we have specified two target labels, first is the label ‘all’ to build executable from myprogram and mylib object files. Let me know if you want to see it.I need someone who is familiar with C/C++ and makefile project to make a simple configuration on my pc: A simple example of the makefile is shown below. It is pretty interesting in how it works. For example, we might create a Makefile for our hello program like this: Makefile for the Hello Program: compile the hello program with compiler warnings, debug info, and include the cs50 library all: hello.c clang -g -Wall -o hello hello.c -lcs50. If you all want to see it, I wrote a simple "Make Anything Makefile" for use at Rutgers (using GNU Make and Grep) a while back.

so that only the object files that actually need recompiling are recompiled.) (In general, the point of a makefile is not to do that. File names determine which implicit rules are run. For example, there is an implicit rule for C compilation. Implicit rules tell make how to use customary techniques so that you do not have to specify them in detail when you want to use them. Notice how the 'all' target builds the program then gets rid of everything except the final executable? Whether or not this is done is up to you. For example, one customary way to make an object file is from a C source file using the C compiler, cc. And the phony targets 'clean' and 'cleanest' get rid of leftover stuff. The other rule (or rules if more than one object file is involved) simply compile individual object files. Notice that the first rule after 'all' was to link the program from the compiled object files. $^ name of all prerequisites with duplicates removed The typical form for a make file is something like:Ĭertain things have special name of the target Since the purpose of the makefile is to compile a specific program, there is no need to put the program's name in a variable. You should avoid trying to use a variable in the name of a pattern target - like $(MYPROGRAM). When you are done, you should see something like:Ģ0 $(CC) $(CFLAGS) $(SOURCE) -o octhecdec $(LDFLAGS) W tym samouczku C ++ Makefile omwimy gwne aspekty narzdzia Make i Makefile, w tym jego zalety i zastosowania w C ++: W kadym projekcie C ++ jednym z wanych celw jest uproszczenie budowania projektu, tak abymy otrzymali wszystkie zalenoci i pliki projektu w jednym miejscu i wykonali je za jednym razem, tak aby uzyska podane dane wyjciowe za. The same thing can be said of MYINCLUDES. Follow the wizard to specify the commands and environment used by your makefile. In Visual Studio 2017 and later, the Makefile project template is available when the C++ Desktop Development workload is installed. To create a makefile project with the makefile project template. (That is, you'll list more than one library, like FLTK and the C math library.) This will produce a command line terminating in: Visual Studio 2019 and later: Create a UNIX makefile project for Linux.

In particular, your MYLIBRARIES variable is dangerous - because at some point you'll want to do something like

C MAKEFILE EXAMPLE FULL

Note that full names (with extensions) of source, object and binary files are used as target and dependent names: define macros EXECUTABLENAME myapp.exe main.obj : main.cpp echo. This program consists of three files main.cpp, factorial.cpp and hello.cpp. Here is yet another example of a simple makefile which compiles single main.cpp into main.obj and then links obj file to myapp.exe. Your choice of variable names could be improved. Makefile - Example, This is an example of the Makefile for compiling the hello program. Since you are using GNU tools, you might as well stick with GNU Make - which is superior to other Make tools in many ways. The best place to start is actually with the documentation.

0 kommentar(er)

0 kommentar(er)